הורדת E-book

מלאו את פרטיכם, וקבלו אליכם לתיבת המייל

קישור להורדת:

Bridging Wireless Communications

Design and Testing with MATLAB

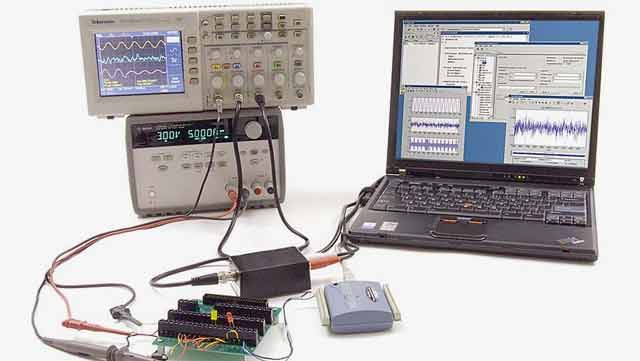

Design and Test Hardware

MATLAB ו-Simulink מאפשרים להטמיע את מערכות התקשורת האלחוטיות שתוכננו בעזרתם על גבי חומרה. בין היתר ניתן לחבר רכיבי RF ו-SDR לשידור או קליטה של אותות, אפשר להשתמש

ב-Wireless Testbench, לצורך שידור וקליטת נתונים במהירות גבוהה ואף ליצור באופן אוטומטי קוד HDL קריא להטמעה על FPGA, SoC, ו-ASIC.