שילוב קוד HDL קיים בתוך סימולציית Simulink

ידוע כי תוכנת Simulink משמשת באופן נרחב בתעשייה למידול, בדיקה ווריפיקציה של מערכות אלקטרוניות מורכבות. בפוסט הזה נתאר את תהליך העבודה לחיבור קוד שכתוב ב -VHDL לסביבת Simulink, ונסביר כיצד להתאים בין סוגי הנתונים וקצבי הדגימה כדי להשיג ביצועים אופטימליים.

אבל האם ידעתם כי ניתן לשלב במודלי Simulink גם קוד VHDL או Verilog וכך להכניס לתוך המודלים הדמייה של רכיבי חומרה שפותחו בעבר או שנרכשו מספקים אחרים? כלי ה-HDL Verifier מאפשר אינטגרציה חלקה בין הקודים הללו על ידי יצירת ממשק עם סימולטורי HDL.

כשרוצים לשלב קוד HDL קיים או כשצריך לבצע ווריפיקציה לקוד HDL, בין אם זה קוד שנוצר באופן ידני או באופן אוטומטי, ולוודא שהוא עובד כפי שמצופה ממנו ברמת המערכת, אפשר להשתמש ב-HDL Verifier על מנת לבצע קוסימולציה שתשלב את סימולצית המודל ב-Simulink יחד עם סימולצית קוד ה-HDL בסימולטור ה-HDL כגון questa, ModelSim, Vivado, XCelium ועוד.

אחת הדרכים הפשוטות לעשות זאת ושאותה נדגים בפוסט הזה היא באמצעות ה-Cosimulation Wizard.

ה-Cosimulation Wizard הוא ממשק משתמש גרפי שמעביר אותנו דרך השלבים השונים שנחוצים על מנת לבצע את הסימולציה המשולבת, מעתה ואילך נכנה אותו בפוסט הזה "אשף הקוסימולציה".

בדוגמה הזו נשתמש ב-Simulink ובסימולטור HDL על מנת לבצע ווריפיקציה לקוד שמממש raised cosine filter ושנכתב בשפת Verilog, קישור לדוגמה הזו מופיע בסוף הדף, באזור הקישורים.

במסגרת הדוגמה האשף יקבל כקלט את קובץ ה-Verilog, ביחד עם נתונים נוספים שנכניס אליו בהמשך וייתן כפלט בלוק Simulink שייצג את קוד ה-HDL. הבלוק הזה יחובר כחלק ממודל ה-Simulink שלנו.

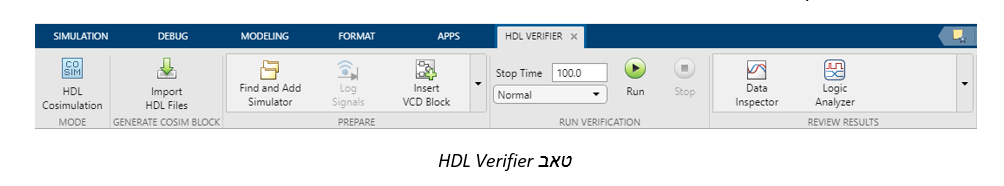

איך מריצים את ה-Cosimulation Wizard? זה פשוט מאוד. נכנסים לטאב Apps ב-Simulink ולוחצים על HDL Verifier. ברגע שנעשה זאת יתווסף לנו טאב נוסף בחלון בשם HDL Verifier. אם נלחץ על הטאב הזה נראה באזור של Mode את האפשרות לבחור HDL Cosimulation, נבחר באפשרות הזו ואז נלחץ על Import HDL Files .

איך מקנפגים את ה-HDL Cosimulation Block עם אשף הקוסימולציה? שאלה מעולה!

נעבור צעד-צעד:

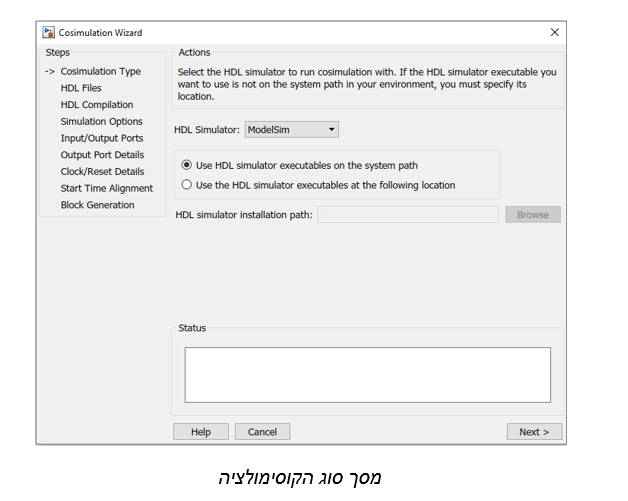

נתחיל ב-Cosimulation Type. וכאן נבחר את סימולטור ה-HDL שבו אנחנו רוצים להשתמש.

אם התיקייה שבה מותקן הסימולטור לא נמצאת ב-path של MATLAB אז ניתן לכתוב כאן גם את הנתיב לתיקיה.

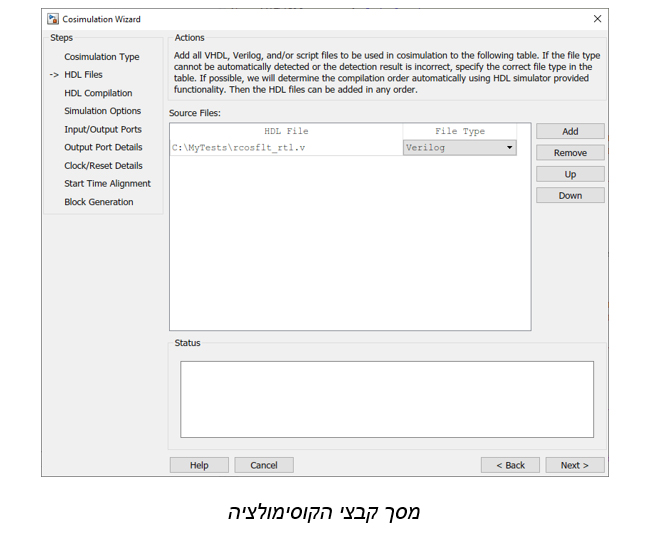

אחרי שנלחץ על Next נגיע לשלב הבא – HDL Files. וכאן על ידי לחיצה על הכפתור “Add” נבחר את קובץ הVerilog- או VHDL ואז נלחץ שוב על הכפתור “Next”.

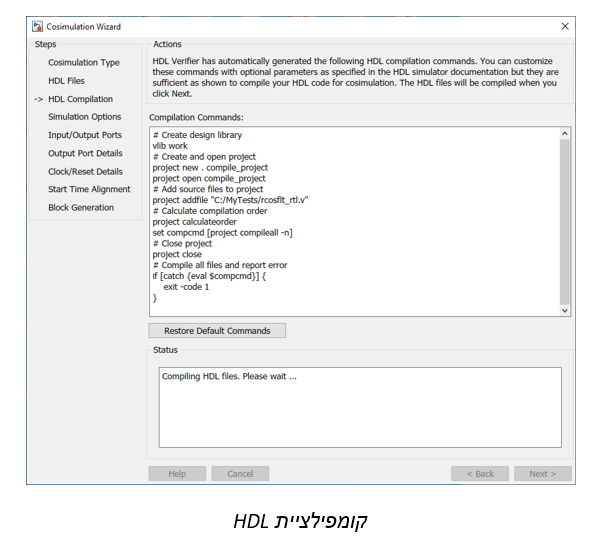

נגיע לשלב HDL Compilation שבו יוצגו פקודות ברירת המחדל לקומפילציה, במידת הצורך ניתן להוסיף או לשנות כאן את פקודות הקומפילציה.

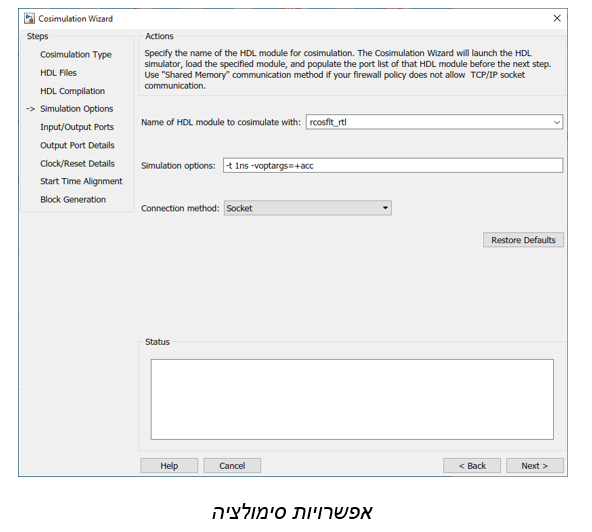

לחיצה על Next תעביר אותנו לשלב Simulation Options, במסך הזה נכניס את שם מודול ה-HDL, ומה שיטת התקשורת אליו.

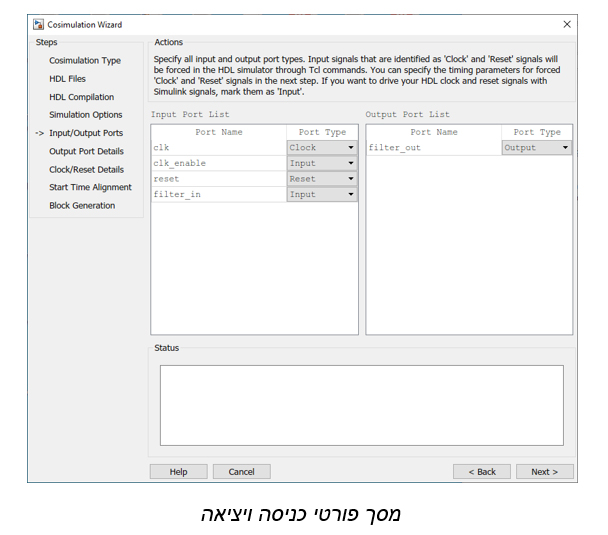

לחיצה על Next ונגיע למסך שבו נגדיר את הפורטים של הכניסות והיציאות.

אשף הקוסימולציה מנסה לזהות את היציאות באופן אוטומטי. אם האשף מזהה יציאה בצורה שגויה, אז אנחנו יכולים לתקן ולשנות את סוג היציאה באופן ידני. עבור כניסות קלט ניתן לבחור בין האפשרויות Clock, Reset, Input או Unused. רק הכניסות שמסומנות כInput- יחוברו ל-Simulink במהלך הקוסימולציה ורק יציאות שמסומנות כ-Output יחוברו לSimulink- במהלך הקוסימולציה. Simulink יתעלם מיציאות שיסומנו כ-Unused.

ניתן לשנות את הפרמטרים של האותות שמסומנים כ-Clock ו-Reset, נראה איך עושים זאת בשלב מאוחר יותר.

בדוגמה שלנו נקבל את סוגי היציאות המוגדרים כברירת מחדל מבלי לשנות ונלחץ על Next על מנת להמשיך לדף פרטי יציאת פלט.

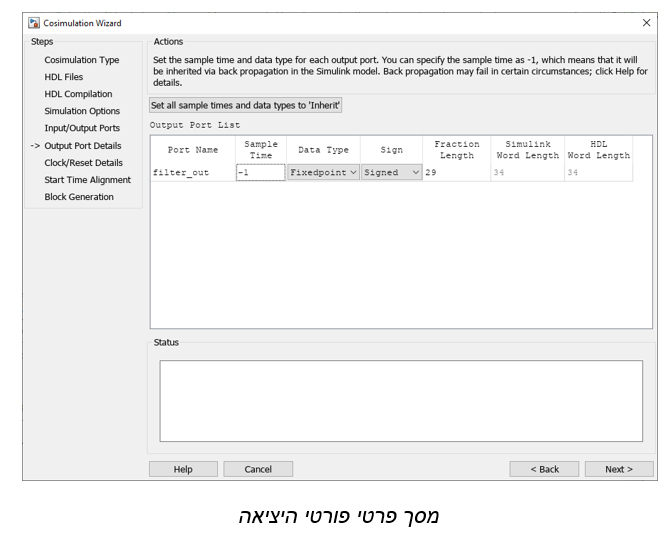

בדף פרטי יציאת פלט נבצע את השלבים הבאים:

קודם כל נגדיר את זמן הדגימה של filter_out עם הערך "-1" שמסמן שהערך יוגדר באמצעות back propagation.

לאחר מכן, אם נפתח את קוד ה-Verilog נוכל לראות שהפלט מופיע בפורמט sfix34_En29 . על כן נשנה את השדות הבאים:

- את ה-Data Type נשנה ל-Fixedpoint

- את הערך של sign, שמגדיר האם יש או אין סימן לערך האות, נשנה ל-Signed

- את אורך השבר נשנה ל-29

נלחץ על הכפתור next כדי להמשיך לדף פרטי ה-clock/reset.

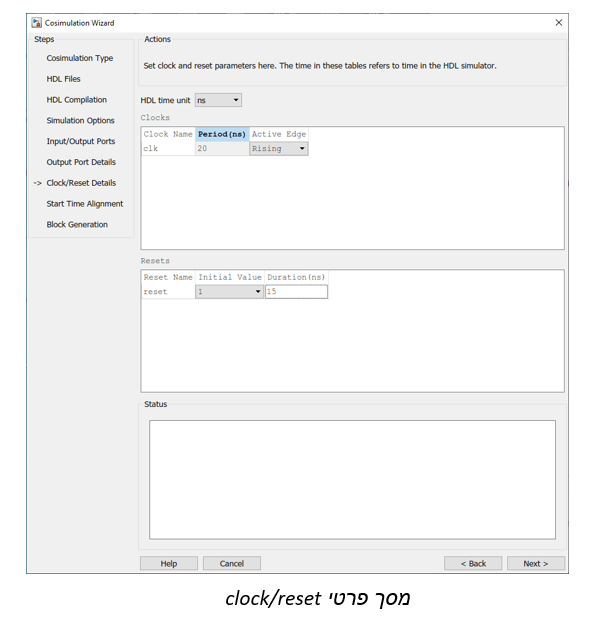

בדף clock/reset בצע את הפעולות הבאות:

אם סימולטור ה-HDL שאיתו נעבוד הוא ModelSim או Xcelium:

- נגדיר את יחידת הזמן HDL ל-ns ואת ה-Clock period ל-20.

- נגדיר את הActive Edge- ל Rising. ואת הreset initial value- ל-1.

- נגדיר את משך ה-reset signal ל-15.

אם סימולטור ה-HDL שאיתו נעבוד הוא Vivado:

- נגדיר את יחידת הזמן HDL ל-ps ואת ה-Clock period ל-20.

- נגדיר את הActive Edge- ל-Rising ואת הreset initial value- ל-1.

- נגדיר את משך ה-reset signal ל-15.

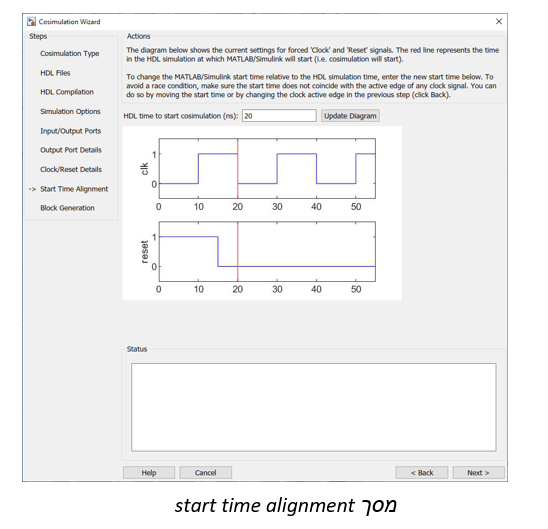

לחיצה על Next כדי להמשיך למסך Start time alignment.

במסך Start time alignment מוצג גרף עבור צורות הגל של האותות clock ו-reset. אשף הקוסימולציה מציג את זמן ה-HDL להתחלת הקוסימולציה באמצעות קו אדום. זמן ההתחלה הוא גם הזמן שבוSimulink מקבל את דגימת הקלט הראשונה מסימולטור ה-HDL.

נגדיר את ה-alignment. השעון שלנו הוא rising edge, על כן בזמן 20ns (ב ModelSim-או Xcelium) או 20 ps (בסימולטור Vivado) הפלט של המסנן יציב ואין צורך לשנות את זמן ברירת המחדל לביצוע הקוסימולציה.

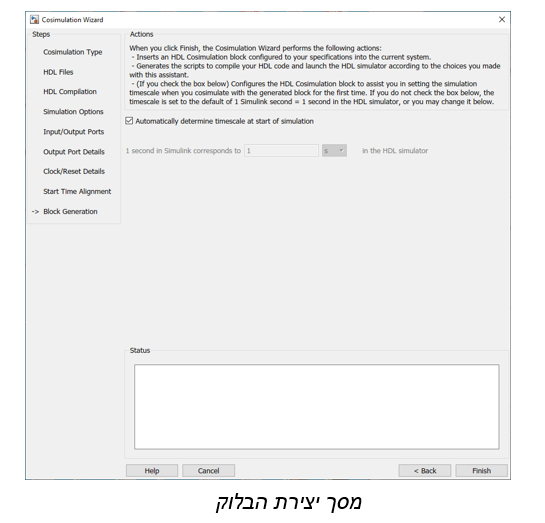

לחיצה על Next תעביר אותנו למסך האחרון באשף, יצירת בלוק ה-HDL Cosimulation.

לפני שיוצרים את הבלוק יש לנו אפשרות לקבוע את ה-timescale. לחלופין, ניתן לבצע זאת מאוחר יותר, לפני הפעלת הסימולציה.

בדף יצירת הבלוק נבצע את השלבים הבאים:

בעבודה עם הסימולטוריםModelSim או Xceliumנשאיר את אפשרות ברירת המחדל Automatically determine timescale at start of simulation כאפשרות הנבחרת. מאוחר יותר, לפני שנריץ את הסימולציה נוכל להציג את לוח הזמנים המחושב ולשנות את הערכים.

בעבודה עם סימולטור Vivado נוריד את הסימון מהאפשרות הזו ונקבע את ה-timescale כך ששנייה אחת ב-Simulink תתאים ל-2e-11 שניות בסימולטור ה-HDL.

לחיצה על Finish תשלים לנו את הפעלת אשף הקוסימולציה ותסגור את החלון.

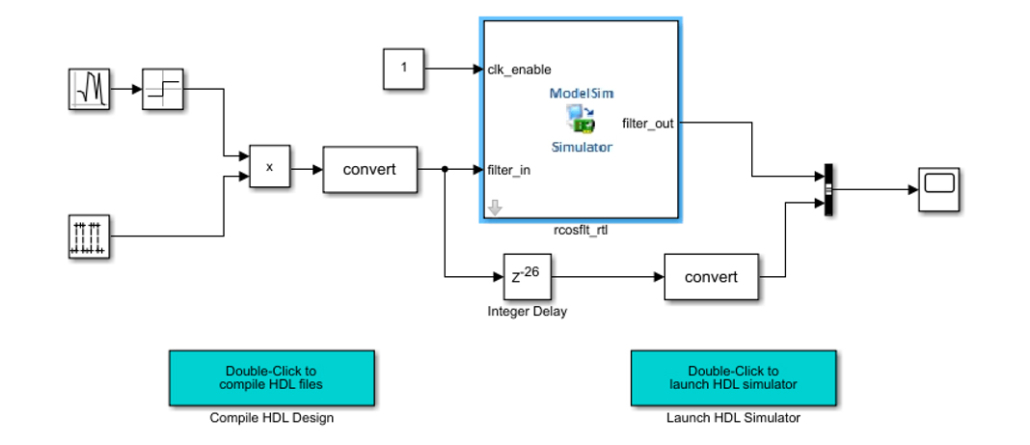

כעת, לאחר שהאשף סיים את עבודתו, הוא יצר לנו את הפריטים הבאים בקנבס של המודל:

- בלוק HDL Cosimulation

- בלוק לריקומפילציה של מודל ה-HDL (מכיל קישור לסקריפט המופעל על ידי לחיצה כפולה על הבלוק)

- בלוק להפעלת סימולטור HDL (מכיל קישור לסקריפט המופעל על ידי לחיצה כפולה על הבלוק) עבור Modelsim ו-Xcelium בלבד.

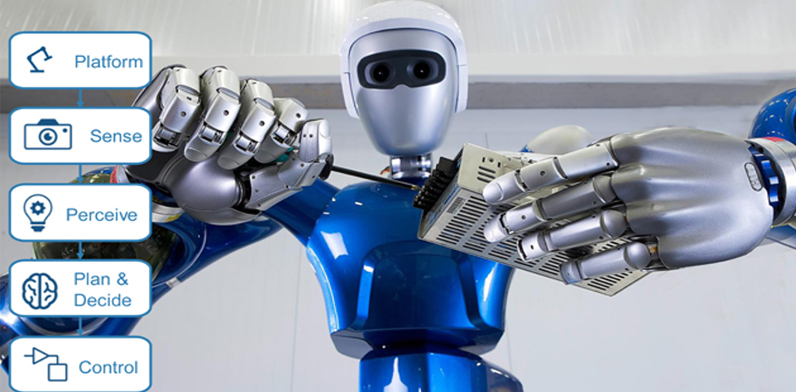

נמקם את בלוק ה-HDL Cosimulation ונחבר אליו את שאר הבלוקים, כך שהמודל שלנו ייראה דומה לזה שבתמונה:

כעת נפעיל את הקוסימולציה

נפעיל את סימולטור HDL על ידי לחיצה כפולה על הבלוק שכותרתוLaunch HDL Simulator ולאחר שהסימולטור עלה נחזור ל-Simulink ונפעיל את הסימולציה

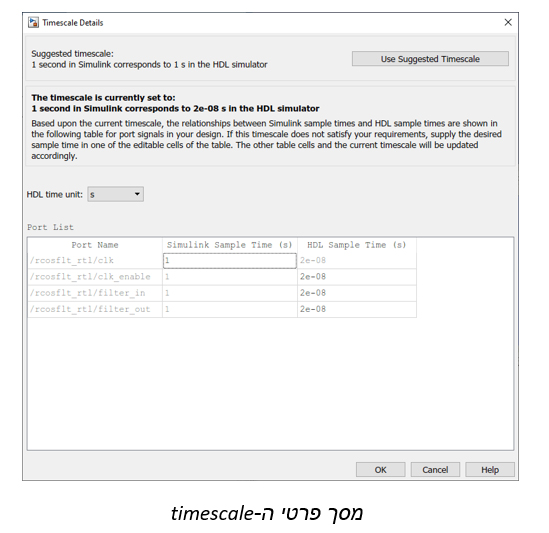

נזכור שבדף האחרון של אשף הקוסימולציה בחרנו לקבוע את ה-timescale לפני הפעלת הסימולציה. על כן לפני ההפעלה יעלה לנו ממשק שיאפשר לנו לבצע את קביעת הערכים. נרצה לקבוע את הערכים כך ששנייה אחת ב-simulink תתאים לזמן מחזור אחד ב-HDL, כלומר 20ns.

נאשר את השינויים ונפעיל מחדש את הסימולציה.

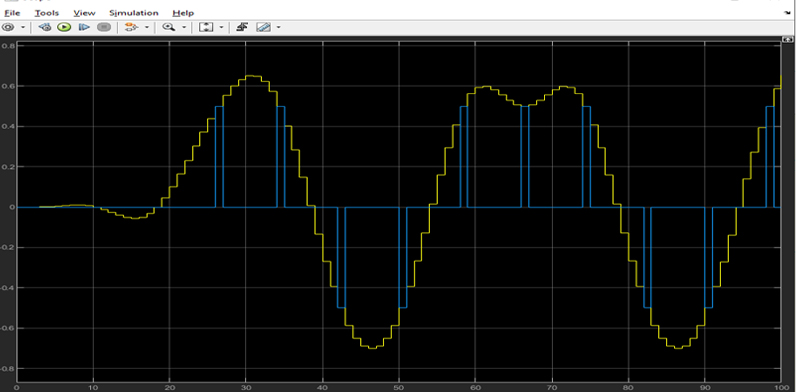

וזהו. הצלחנו להפעיל את המודל שלנו ולבצע קוסימולציה של המודל ב-Simulink יחד עם קוד ה-HDL הקיים שלנו ובדרך זו נוכל הן לעשות ווריפיקציה לקוד ה-HDL והן reuse עבור קוד שכבר קיים לנו ואנחנו יודעים שהוא מאומת ועובד, ורוצים לשלב אותו כחלק מהסימולציה. התמונה בראש העמוד היא מתוך ה-scope בדוגמה שמחוברים אליו אות הכניסה ואות היציאה מה-HDL cosimulation block.

למידע נוסף:

Simulink Cosimulation – מתוך הדוקומנטציה של Simulink

Import HDL for Cosimulation with Simulink – וובינר של MathWorks בנושא

HDL Cosimulation – מתוך הדוקומנטציה של ה-HDL Verifier

Get Started with Simulink HDL Cosimulation – הדוגמה שראינו